Fundamental, testul in-circuit se bazează pe posibilitatea de acces fizic la nodurile electrice ale PCB-ului. Tehnologia SMD a avut un impact serios in abilitatea de plasare cu acurateţe a pad-urilor de testare. Device-urile SMD şi PCB-urile multistrat au făcut ca accesul fizic la nodurile electrice să fie serios limitat.

Miniaturizarea plăcilor electronice face ca anumite componente SMD să aibă pinii foate apropiaţi, iar accesul la aceşti pini pentru testare este dificil, spaţiul util fiind sub 25 mils (0.6 mm). De asemenea, structura internă a IC-ului poate fi foarte complicată fiind necesari milioane de vectori de test pentru o testare integrală. Sesizand acest trend la mijlocul anilor 80' un grup de ingineri de test a examinat posibilitatea testării plăcilor electronice care prezintă acces limitat la nodurile electrice. Soluţia propusă a avut la bază accesul la pinii circuitelor integrate folosind un registru de deplasare conectat intern la toţi pinii componentei. Tehnologia a fost denumită “Boundary Scan”.

Organizaţia care a dezvoltat standardul Boundary Scan - la care au aderat toţi producatorii de componente - se numeşte Join Test Action Group (JTAG). Această tehnologie a fost standardizată internaţional şi a primit codul IEEE1149.1-1990, fiind publicată prima dată in 1990. Astăzi, ea este cunoscută sub numele Boundary Scan sau JTAG.

Principiul de lucru Boundary Scan (JTAG)

Un circuit integrat ce conţine structură de tip Boundary Scan are adăugat la fiecare pin de intrare sau de ieşire un element suplimentar de memorie de 1 bit (0 sau 1 logic) care se numeşte celulă Boundary Scan. Această celulă poate capta informaţia de nivel logic de la un pin de input sau poate scrie un nivel logic la un pin de output. Celulele de memorie sunt inlănţuite formand un registru serial, astfel că ele pot permuta date secvenţial pornind de la un pin standard de intrare TDI (Test Data In) sau pot transmite date colectate serial printr-un pin standard dedicat numit TDO (Test data Out).

Transmisia şi recepţia datelor se face sincronizat folosind un pin de clock TCK (Test Clock), iar modurile de operare in regim de testare sunt controlate prin pinul TMS (Test Mode Select).

Comportamentul celulelor scanate şi logica de lucru Boundary Scan este controlată prin intermediul unui controler dedicat numit TAP controller (Test Access Port controller). Pinul opţional TRST (Test Reset) ne permite să resetăm logica de testare Boundary Scan independent de structura logică funcţională a circuitului integrat. Este foarte important de reţinut că la nivelul circuitului integrat elementele de testare Boundary scan (celule de memorie, pinii TDI, TDO, TMS, TCK, TRST, TAP controller) sunt total separate de structura logică a circuitului integrat şi nu o influenţează in nici un fel.

Firmele care produc circuite integrate ce conţin această tehnologie furnizează gratuit descrierea modelului comportamental in regim de autotestare Boundary Scan, pentru fiecare circuit integrat in parte sub forma unui fişier cu extensia *.BDSL.

In cazul in care există mai multe componente de tip Boundary Scan ele sunt interconectate din faza de design a plăcii electronice şi astfel se creează un lanţ de tip Boundary Scan. In cazul de faţă avem 4 IC-uri, pinul de ieşire serial TDO al IC1 este conectat la pinul de intrare serial TDI al IC2, pinul TDO al IC2 este conectat la pinul TDI al IC3, pinul TDI al IC4 este conectat la pinul TDO al IC3. Practic s-a creat un lanţ de transmisie serială a informaţiei de la pinul TDI al IC1 la pinul TDO al IC4.

Pinii de clock TCK sunt conectaţi in paralel la toate IC-urile. Pinii de selecţie TMS sunt conectaţi in paralel la toate IC-urile.

Pinii TDI, TDO, TCK, TMS ai PCB-ului sunt conectaţi prin intermediul unei interfeţe standard la un computer ce rulează un software de aplicaţie Boundary Scan. Acest software sesizează prezenţa celor 4 IC-uri cu celule Boundary Scan, furnizează serial vectori de testare şi compară informaţia transmisă prin pinul TDI al lui IC1 cu informaţia recepţionată prin pinul TDO al IC-ului IC4, la o frecvenţă setată variabilă. (maxim 50MHz).

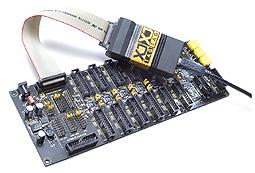

PCB demo şi Interfaţa XJ Link de la XJTAG

Alimentarea plăcii electronice se face fie direct din interfaţa USB (dacă permite schema) sau separat.

Astfel, se pot realiza patru operaţiuni de bază: incărcarea unei informaţii prin permutare serială (shift-in), prin pinul TDI; aplicarea unui stimul pe un anumit pin (update); capturarea nivelului logic de pe un anumit pin (capture); recepţionarea unei valori de la un anumit pin serial prin pinul TDO. Practic aceste celule boundary scan au rolul unor pini de test virtuali şi permit execuţia următoarelor tipuri de teste:

- verificarea tipului, a producătorului şi a versiunii circuitelor integrate (ID code pe 32 de biţi);

- diagnoza rapidă a scurt-circuitelor, intreruperilor pentru IC-urile altfel inacesibile (Extest);

- izolarea componentelor prin punerea pinilor in stare de impedanţă ridicată fără a utiliza tehnologia ICT clasică de backdriving;

- programarea datelor serial şi verificarea lor;

- testarea altor componente care sunt conectate la pinii circuitelor integrate cu Boundary scan prin folosirea acestora ca pini virtuali.

Software-ul dezvoltat de firma XJTAG (www.xjtag.com) - specializată in soluţii de test Boundary Scan ce rulează in mediul Windows 2000/XP/Vista este format din următoarele module:

1 XJ Runner - modulul operator, in care paşii de test executaţi sunt vizibili pe monitor, iar mesajul de valid/defect este dat la nivel de componentă.

2 XJ Analyzer - Modulul de software de analiză şi debug - permite recunoaşterea automată a tipului de componentă şi vizualizarea stării pinilor tuturor circuitelor integrate din lanţul Boundary Scan in timpul testării.

Culoarea pinilor specifică valoarea lor curentă, iar starea pinilor se poate seta pentru pinii de output şi cei bidirecţionali in “1” logic, “0” logic, oscilare rapidă şi oscilare lentă. De asemenea, se poate selecta vizualizarea semnalelor de la componente diferite sub formă de tabel, astfel incat putem analiza funcţionarea PCB-ului in diverse regimuri.

3 XJ Ease - modul compilator al codului de testare, utilizat pentru:

- generarea testelor de interconectare;

- programarea circuitelor integrate Boundary Scan (CPLDs, FPGAs);

- programarea circuitelor integrate ce nu sunt standard Boundary Scan (memorii flash);

- testarea circuitelor integrate ce nu sunt standard Boundary Scan, dar care sunt conectate la pinii de test virtuali Boundary Scan: pentru aceste componente se creează intr-un limbaj propriu librării (XJ Ease device files) care pot fi apelate de mai multe ori in acelaşi proiect sau pot fi folosite in proiecte ulterioare.

Astfel, avantajul major la XJTAG este mutarea centrului de greutate dinspre generarea de vectori de test spre dezvoltarea de librării de componente, acoperirea unei plăci electronice fiind foarte bună in cazul componentelor non-Boundary Scan.

Pe baza librăriilor existente, compilatorul XJTAG generează vectorii de test adecvaţi in funcţie de pinii virtuali Boundary Scan ai schemei respective.

Concluzie

Putem spune că testul Boundary Scan (JTAG) asigură o testabilitate ridicată a PCB-ului prin utilizarea numai a 5 pini standard de interfaţare utilizandu-se acelaşi test in faza de dezvoltare şi in cea de producţie. Suplimentar de la caz la caz, putem adăuga teste funcţionale şi putem realiza programarea circuitelor integrate, reducand timpii de dezvoltare şi costurile de realizare a programelor de test pentru plăci electronice populate.

.de

.de

Reply With Quote

Reply With Quote